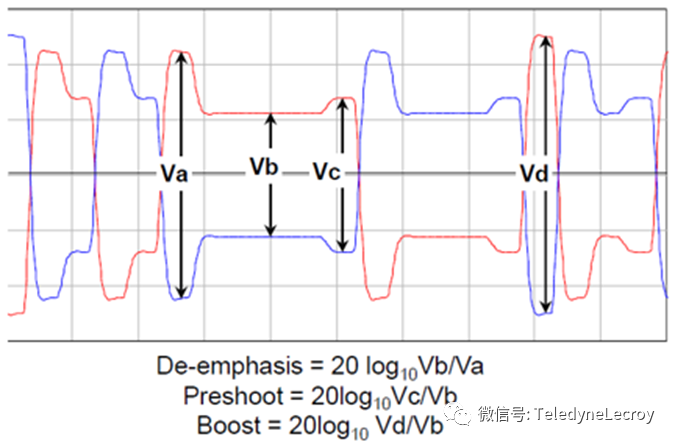

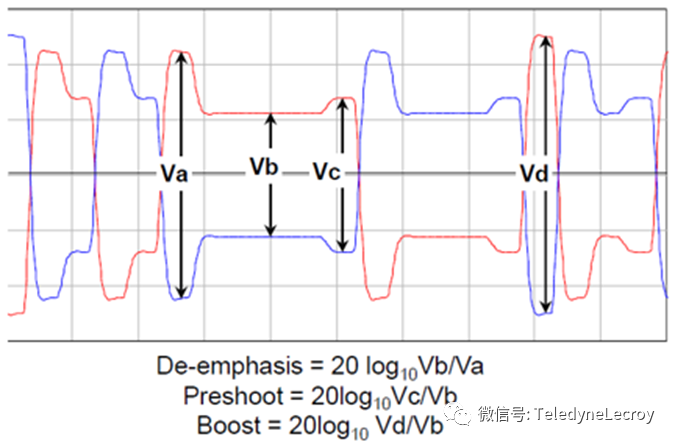

隨著連續(xù)幾代 力科PCIe協(xié)議分析儀 Express 以 8 Gbps、16 Gbps 和 32 Gbps 的速度運(yùn)行�,動態(tài)鏈路均衡變得至關(guān)重要。均衡會補(bǔ)償通信信道對信號的影響����。這些影響包括充當(dāng)?shù)屯V波器的鏈路,它會衰減數(shù)據(jù)流中的關(guān)鍵高頻分量�����,此外����,由連接器和過孔引起的鏈路阻抗不連續(xù)會進(jìn)一步降低鏈路性能。PCIe協(xié)議分析儀均衡可應(yīng)用于發(fā)送端 (TxEQ)����、接收端 (RxEQ) 或兩端都應(yīng)用�����, TxEQ 涉及去加重和預(yù)沖�,而 RxEQ 涉及連續(xù)時間線性均衡 (CTLE) 和判決反饋均衡 (DFE)��。在發(fā)送端����,去加重會使跳變后的第一位以全幅度 (Va) 發(fā)送,相同極性的后續(xù)位以降低的電平 (Vb) 傳輸��,但在下一次跳變之前的最后一位除外���,它以提高的預(yù)沖電平 (Vc) 傳輸����。此外�����,轉(zhuǎn)換之間的單個bit位以最大增強(qiáng)電平 (Vd) 傳輸��。去加重和增強(qiáng)的組合補(bǔ)償了鏈路會衰減的信號高頻成分。均衡涉及多個階段的鏈路訓(xùn)練序列�����,有時會產(chǎn)生意想不到的結(jié)果��。 使用 PCIe協(xié)議分析儀 CrossSync PHY關(guān)聯(lián)協(xié)議層和物理層數(shù)據(jù)的能力可以幫助定位鏈路訓(xùn)練后可能出現(xiàn)的邏輯和電氣問題���。PCIe協(xié)議分析儀鏈路訓(xùn)練過程

發(fā)送端均衡(去加重、預(yù)沖和增強(qiáng))����,是由 PCIe 系統(tǒng)的 TxEQ內(nèi)的三抽頭有限脈沖響應(yīng) (FIR) 濾波器實現(xiàn)。鏈路訓(xùn)練的目標(biāo)是確定給定通信鏈路的最佳 FIR 濾波器系數(shù)���,也稱為游標(biāo)系數(shù)����。鏈路訓(xùn)練在下行端口和上行端口之間交換有序數(shù)據(jù)集�����,包括TS1訓(xùn)練序列和TS2訓(xùn)練序列 ���。 PCIe 鏈路訓(xùn)練是如何運(yùn)行的����?

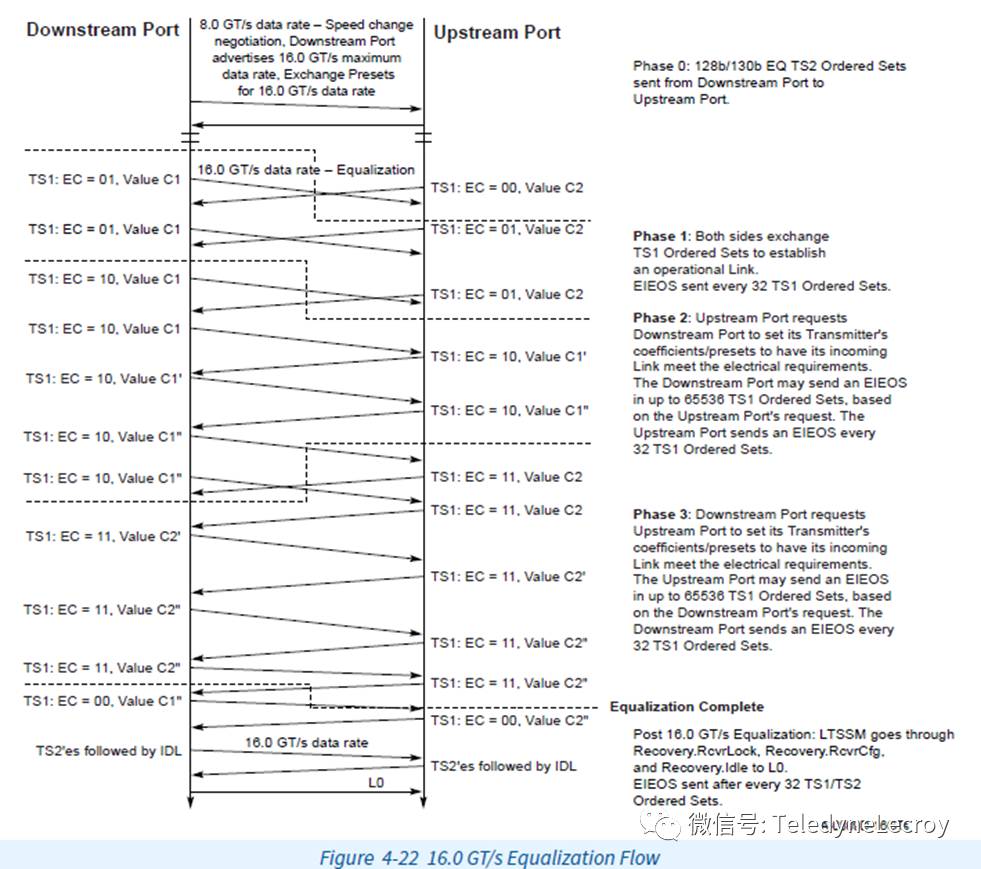

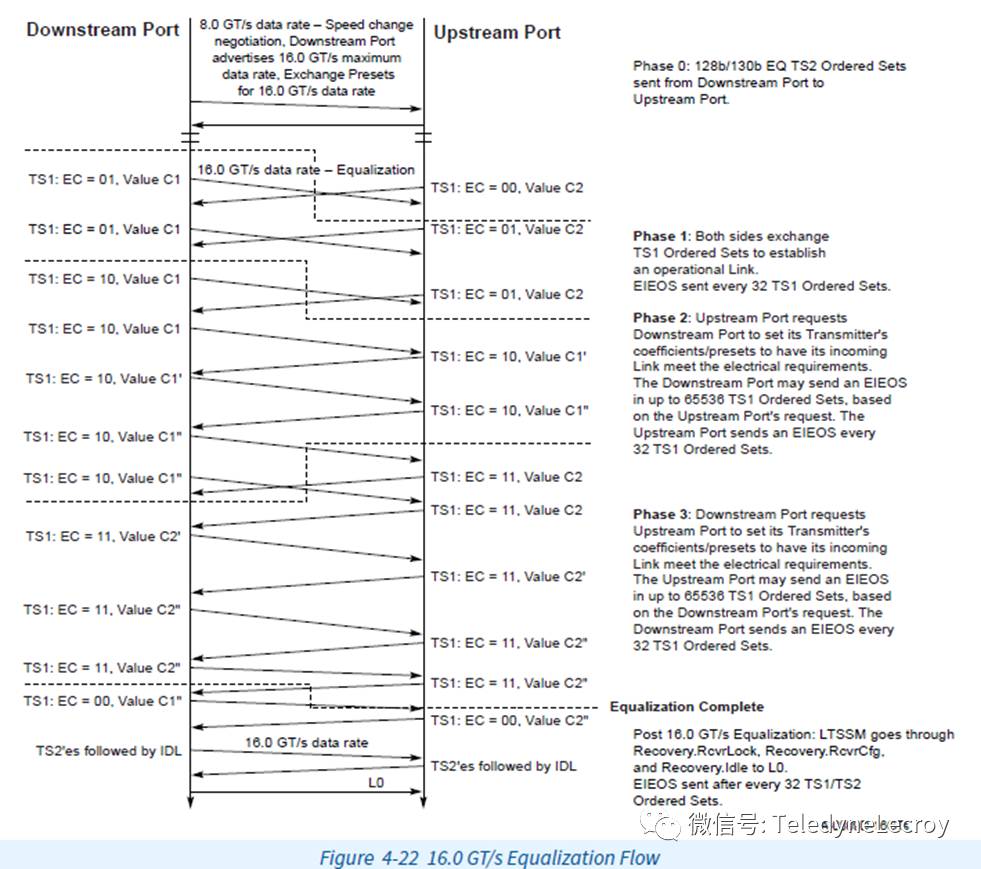

以PCIe4.0協(xié)議分析儀為例,PCIe 4.0 鏈路訓(xùn)練從速度變化協(xié)商開始���,有4個階段����,階段 0 到階段 3���。在階段 0��,下行端口以 8GT/s 數(shù)據(jù)速率向上行端口發(fā)送 TS2 有序集���,通告 16GT/s 的最大數(shù)據(jù)速率。在階段 1�,兩個端口交換 TS1 有序集,在每 32 個 TS1 有序集之后穿插一個電氣空閑退出有序集 (EIEOS)��,以建立操作鏈路��。EIEOS 的目的是保證鏈路伙伴可以檢測到電氣空閑退出狀態(tài)����,EIEOS 數(shù)據(jù)包符號(四個交替的 00 00 FF FF 序列)產(chǎn)生規(guī)則且具有相對較少的轉(zhuǎn)換的電信號���,這對于在調(diào)試期間觀察信號的物理層屬性非常有用。